# Compiling the $\pi$ -calculus into a Multithreaded Typed Assembly Language

Tiago Cogumbreiro Francisco Martins Vasco T. Vasconcelos

DI-FCUL

TR-08-13

$\mathrm{May}\ 2008$

Departamento de Informática Faculdade de Ciências da Universidade de Lisboa Campo Grande, 1749–016 Lisboa Portugal

Technical reports are available at http://www.di.fc.ul.pt/tech-reports. The files are stored in PDF, with the report number as filename. Alternatively, reports are available by post from the above address.

## Compiling the $\pi$ -calculus into a Multithreaded Typed Assembly Language

Tiago Cogumbreiro — Francisco Martins Vasco T. Vasconcelos

$\mathrm{May}\ 2008$

#### Abstract

Current trends in hardware made available multi-core CPU systems to ordinary users, challenging researchers to devise new techniques to bring software into the multi-core world. However, shaping software for multi-cores is more envolving than simply balancing workload among cores. In a near future (in less than a decade) Intel prepares to manufacture and ship 80-core processors; programmers must perform a paradigm shift from sequential to concurrent programming and produce software adapted for multi-core platforms.

In the last decade, proposals have been made to compile formal concurrent and functional languages, notably the  $\pi$ -calculus, typed concurrent objects, and the  $\lambda$ -calculus, into assembly languages. The last work goes a step further and presents a series of type-preserving compilation steps leading from System F to a typed assembly language. Nevertheless, all theses works are targeted at sequential architectures.

This paper proposes a type-preserving translation from the  $\pi$ -calculus into MIL, a multithreaded typed assembly language for multi-core/multi-processor architectures. We start from a simple asynchronous typed version of the  $\pi$ -calculus and translate it into MIL code that is then linked to a runtime library (written in MIL) that provides support for implementation of the  $\pi$ -calculus primitives (e.g., queuing messages and processes). In short, we implement a message-passing paradigm in a shared-memory architecture.

## Contents

| 1 | Introduction                                     | 2           |

|---|--------------------------------------------------|-------------|

| 2 | The $\pi$ -Calculus 2.1 Syntax                   | 4<br>5<br>6 |

| 3 | MIL: Multithreaded TAL  3.1 Architecture         | 11<br>12    |

| 4 | The $\pi$ -Calculus Run-time 4.1 Channels Queues | 32          |

| 5 | Translating the $\pi$ -calculus into MIL         | 46          |

| 6 | Conclusion                                       | <b>54</b>   |

| ٨ | Ougues                                           | 56          |

## Chapter 1

## Introduction

Physical and electrical constrains are limiting the increase of frequency of each processing unit of a processor, thus the top speed of each processing unit is not expected to increase much more in near future. Instead manufactures are augmenting the number of processing units in each processor (multicore processors) to continue delivering performance gains. The industry is making big investments in projects, such as RAMP [21] and BEE2 [1], that enable emulation of multi-core architectures, showing interest in supporting the foundations for software research that targets these architectures.

To take advantage of multi-core architectures, parallel and concurrent programming needs to be mastered [19]. With the advent of major availability of parallel facilities (from embedded systems, to super computers), programmers must do a paradigm shift from sequential to parallel programming and produce, from scratch, software adapted for multi-core platforms.

The MDA (Model-Driven Architecture) / MDE (Model-Driven Engineering) methodologies are being widely used for software system development [18, 9]. However, these methodologies have informal specification languages and lack semantic foundations. The concurrency theory results (e.g. operational semantics, or axiomatic semantics) might enhance these methodologies [5].

In the last decade, some proposals have been made to compile concurrent and functional languages, notably the  $\pi$ -calculus [23], typed concurrent objects [11], and the  $\lambda$ -calculus [17], into assembly languages. The last work goes a step further and presents a series of type preserving compilation steps leading from System F [6] to a typed assembly language [17]. Yet, all the works are targeted for systems with a single core CPU architecture.

We propose a typed preserving translation from the  $\pi$ -calculus into MIL, a multithreaded typed assembly language aiming at multi-core/multi-processor architectures. We depart from a simple asynchronous typed version of the  $\pi$ -calculus [2, 8, 16] and translate it into MIL, based on a run-time library (written in MIL) that provides support (e.g. queueing of messages and processes) for implementation the  $\pi$ -calculus primitives.

The run-time library defines channels and operations on channels to send and to receive messages. Messages are buffered in the channel they are sent to, until a process request for a message in the channel. The reverse is also true to processes: a process requesting for a message gets blocked until another one sends a message, by storing their state and their code in the channel.

The run-time library and the translation function have an intertwined design, although there is a clear separation of concerns between them. The concept of a process is traversal and defined at different levels of abstraction in both parts.

The concurrency is also preserved to a certain extent (limited only by the number of available processors):  $\pi$  processes are represented by MIL threads of execution. The concurrent architecture of the target language is, therefore, extensively explored, resulting in highly parallel programs free of race-conditions.

This paper is divided into seven chapters. Chapter 2 describes the  $\pi$ -calculus, the source language. Chapter 3 presents our target language, MIL. Chapter 4 and Chapter 5 discusses the translation from the  $\pi$ -calculus into MIL. Finally, in Chapter 6, we summarize our work and hint at future directions.

## Chapter 2

## The $\pi$ -Calculus

The  $\pi$ -calculus, developed by Robin Milner, Joachim Parrow, and David Walker [16], is a process algebra for describing *mobility*. The  $\pi$ -calculus is used to model a network of interconnected processes interacting through connection links (ports) by sending and receiving references to other processes, thus allowing the dynamic reconfiguration of the network.

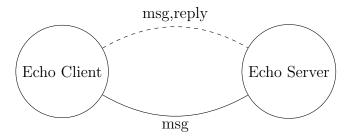

As an example, consider a process that bounces every message received in a port. Figure 2.1 depicts such an interaction. The client sends message msg and a reply channel, where the server should echo the message to the client. Afterwards, the server sends the message msg back to the client.

In this chapter we present an overview of the  $\pi$ -calculus syntax and semantics.

Figure 2.1: The server echoing the received message back to the client. The dashed line represents communication from the client to the server. The full line represents communication from the server to the client.

```

Processes

Values

P, Q ::= 0

nil

name

v ::=

x, y

\overline{x}\langle \vec{v}\rangle

output

basval basic value

| x(\vec{y}).P

input

P \mid Q

parallel

(\nu x: (\vec{T})) P

restriction

!P

replication

```

The syntax of T is illustrated in Figure 2.3

Figure 2.2: Process syntax

#### 2.1 Syntax

**Processes.** The adopted  $\pi$ -calculus syntax is based on [15] with extensions presented in [22]: asynchronous, polyadic, and typed.

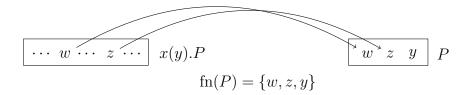

The syntax, depicted in Figure 2.2, is divided into two categories: names and processes. Names are ranged over by lower case letters x and y. Values, v, symbolise either names or primitive values. A vector above a symbol abbreviates a possibly empty sequence of these symbols. For example  $\vec{x}$  stands for the sequence of names  $x_0 \dots x_n$  with  $n \geq 0$ . Processes, denoted by upper case letters P and Q, comprise the nil process,  $\mathbf{0}$ , corresponding to the inactive process; the output process,  $\overline{x}\langle \vec{v}\rangle$ , outlines the action of sending data,  $\vec{v}$ , through a channel x; the input process,  $x(\vec{y}).P$ , that receives a sequence of values via channel x and continues as P, with the received names substituted for the received values; the parallel composition process,  $P \mid Q$ , represents two active processes running concurrently; the restriction process,  $(\nu x: (\vec{T})) P$ , that creates a new channel definition local to process P; and finally the replicated process, P, that represents an infinite number of active processes running in parallel.

The following example is a possible implementation of the echo server depicted in Figure 2.1.

$$!echo(msg, reply).\overline{reply}\langle msg\rangle$$

(2.1)

This process is ready to receive a message msq and a communication channel

```

Types \qquad \qquad Basic\ value\ types T,S::= B \quad \text{basic\ value\ type} \qquad B::= int \quad \text{integer\ type} \mid (\vec{T}) \quad \text{link\ type} \qquad \mid str \quad \text{string\ type}

```

Figure 2.3: Type syntax

reply trough channel echo. After receiving the values, it outputs the message through channel reply. The process is replicated because is must be able to communicate with multiple clients.

**Types.** Types are assigned to channels and to basic values. A basic value type is either a string, str, or an integer, int; the channel type  $(\vec{T})$  describes the types of the communicated value  $\vec{T}$  through the channel. For example, a possible type for the echo channel from Process 2.1 is (str, (str)).

#### 2.2 Semantics

The semantics of the  $\pi$ -calculus expresses formally the behaviour of processes. With a rigorous semantics we can identify if two processes have the same structural behaviour, observe how a process evolves as it interacts, and analyse how links move from one process to another.

For the sake of clarity, we omit the type from the restriction operator.

Structural Congruence. The structural congruence relation,  $\equiv$ , is the smallest congruence relation on processes closed under rules given in Figure 2.4. Structural congruence identifies processes that represent the same behaviour structure and can be used to reshape process structure to enable reduction. The rules are straightforward. Rule S1 allows for alpha-conversion; Rules S2, S3, and S4 are the standard commutative monoid laws regarding parallel composition, having  $\bf 0$  as neutral element; Rule S5 allows for scope extrusion; Rule S6 garbage collects unused names; Rule S7 states that restriction order is of no importance; and finally Rule S8 allows replication to unfold.

(S1) change of bound names

(S2)

$$P \mid \mathbf{0} \equiv P$$

,  $P \mid Q \equiv Q \mid P$ ,  $P \mid (Q \mid R) \equiv (P \mid Q) \mid R$

(S3)

$$(\nu x: (\vec{T})) (P \mid Q) \equiv P \mid (\nu x: (\vec{T})) Q$$

if  $x \notin \text{fn}(P)$

(S4)

$$(\nu x: (\vec{T})) \mathbf{0} \equiv \mathbf{0}$$

(S5)

$$(\nu x: (\vec{T})) (\nu y: (\vec{S})) P \equiv (\nu y: (\vec{S})) (\nu x: (\vec{T})) P$$

, if  $x \neq y$

(S6)

$$!P \equiv P \mid !P$$

Figure 2.4: Structural congruence rules

$$\overline{x(\vec{y}).P \mid \overline{x}\langle \vec{v}\rangle \mid Q \to P\{\vec{v}/\vec{a}\} \mid Q} \overset{\text{REACT}}{}$$

$$\frac{P \to P'}{P \mid Q \to P' \mid Q} \overset{\text{PAR}}{} \frac{P \to P'}{(\nu \, x \colon (\vec{T})) \, P \to (\nu \, x \colon (\vec{T})) \, P'} \overset{\text{RES}}{}$$

$$\frac{Q \equiv P \quad P \to P' \quad P' \equiv Q'}{Q \to Q'} \overset{\text{STRUCT}}{}$$

Figure 2.5: Reaction Rules

Bound and free names are defined as usual in the  $\pi$ -calculus, so we omit their formal definitions.

**Reduction.** The reduction relation  $\rightarrow$  defined over processes, in Figure 2.5, establishes how a computational step transforms a process [14]. The formula  $P \rightarrow Q$  means that process P can interact and evolve (reduce) to process Q.

The axiom React is the gist of the reaction rules, representing the communication along a channel [13]. An output process,  $\overline{x}\langle \vec{v}\rangle$ , can interact with an input process,  $x(\vec{y}).P$ , if they have the same channel's name, x. The output message,  $\vec{v}$ , moves along channel x to process P and replaces the entry points,  $\vec{y}$ , resulting  $P\{\vec{v}/\vec{y}\}$ . The term  $P\{\vec{v}/\vec{y}\}$  means that the names  $\vec{y}$ , in process P, are to be replaced by the values  $\vec{v}$ .

$$\frac{baseval \in B}{\Gamma \vdash baseval \colon B} \text{ TV-BASE} \quad \overline{\Gamma, x \colon T \vdash x \colon T} \text{ TV-NAME}$$

$$\frac{\Gamma \vdash D}{\Gamma \vdash 0} \text{ TV-NIL} \quad \frac{\Gamma \vdash P}{\Gamma \vdash !P} \text{ TV-REP}$$

$$\frac{\Gamma \vdash x \colon (T_0 \dots T_i) \quad \Gamma, y_0 \colon T_0, \dots, y_i \colon T_i \vdash P}{\Gamma \vdash x(\vec{y}).P} \text{ TV-IN}$$

$$\frac{\Gamma \vdash x \colon (\vec{T}) \quad \Gamma \vdash v_i \colon T_i \quad \forall i \in I}{\Gamma \vdash \overline{x} \langle \vec{v} \rangle} \text{ TV-OUT}$$

$$\frac{\Gamma \vdash P \quad \Gamma \vdash Q}{\Gamma \vdash P \mid Q} \text{ TV-PAR} \quad \frac{\Gamma, x \colon (\vec{T}) \vdash P}{\Gamma \vdash (\nu \, x \colon (\vec{T})) \, P} \text{ TV-RES}$$

Figure 2.6: Typing rules for the  $\pi$ -calculus

Rule PAR expresses that reduction can appear on the right side of a parallel composition. RES governs reduction inside the restriction operator. Rule STRUCT brings congruence rules to the reduction relation.

Process

$$!echo(msg, reply).\overline{reply}\langle msg \rangle \mid (\nu \, r) \, \overline{echo}\langle \text{'hello world!'}, r \rangle$$

represents, respectively, the echo server being run concurrently with a client that creates a new name r and sends it, along with a message, through channel echo, to the server. The following steps describe the reaction between both processes:

$$!echo(msg, reply).\overline{reply}\langle msg \rangle \mid (\nu \, r) \, \overline{r} \langle \text{'hello world!'} \rangle$$

**Type system.** Figure 2.6 presents a standard type system for the  $\pi$ -calculus.

Rule TV-BASE states that primitive values (strings and numbers) are well typed. Rule TV-NAME sets forth that a name is well typed if it is defined in the type environment and the type used matches the name's declaration. The inactive process  $\mathbf{0}$  is always well typed, rule TV-NIL. The process  $(\nu x: (\vec{T})) P$

is well typed if, by adding the association between name x and type  $(\vec{T})$  to  $\Gamma$ , the contained process P is well typed, rule Tv-Res. Tv-In rules that the input process,  $x(\vec{y}).P$ , is well typed if the name of the input channel, x, is a link type and if, by mapping each name of the input channel's arguments to the corresponding type of x, the contained process, P, is well typed. The output process,  $\overline{x}\langle \vec{v}\rangle$ , is well typed if its name, x, is declared as link type and if its arguments are correctly typed, rule Tv-Out. The consistency of the replicated process depends on the consistency of the process being replicated, rule Tv-Rep. The parallel process is well typed if each of the composing processes are well typed, rule Tv-Par.

Now, we show that process

$$(\nu echo: (str, (str))) echo(msg, reply). \overline{reply} \langle msg \rangle$$

is well typed. Using rule Tv-Res we derive

$$\frac{\emptyset, echo \colon (str, (str)) \vdash echo(msg, reply).\overline{reply} \langle msg \rangle}{\emptyset \vdash (\nu \, echo \colon (str, (str))) \, echo(msg, reply).\overline{reply} \langle msg \rangle} \, \text{Tv-Res}$$

Let  $\Gamma' \stackrel{\text{def}}{=} \emptyset$ , echo: (str,(str)). We need to prove that the new typing environment,  $\Gamma'$ , typifies process

$$echo(msg, reply).\overline{reply}\langle msg \rangle$$

Applying rule Tv-In:

$$\frac{\Gamma', msg \colon str, reply \colon (str) \vdash \overline{reply} \langle msg \rangle \quad \Gamma' \vdash echo \colon (str, (str))}{\Gamma' \vdash echo(msg, reply) . \overline{reply} \langle msg \rangle} \text{ Tv-In}$$

Rule Tv-Name ensures that  $\Gamma' \vdash echo : (str, (str))$  holds. Now, let

$$\Gamma'' \stackrel{\text{def}}{=} \Gamma', msq: str, reply: (str)$$

We are left with the second sequent, that also holds

$$\frac{\overline{\Gamma'' \vdash reply \colon (str)} \ \ \, \overline{\Gamma'' \vdash msg \colon str}}{\Gamma'' \vdash \overline{reply} \langle msg \rangle} \frac{\text{TV-Name}}{\text{TV-Out}}$$

## Chapter 3

# MIL: Multithreaded Typed Assembly Language

MIL [24] combines a typed assembly language (TAL) with multithreaded programming, providing the possibility for "executing trusted code safely and efficiently" [17]. Types ensure that pointers cannot be fabricated or forged and that jumps can only be done to checked code, allowing untrusted compilers to generate a typed assembly language that can be compiled with a single trusted compiler.

Multithreaded programming at assembly level helps structuring interthread synchronisation. The type system we provide for the language enforces the absence of race conditions.

#### 3.1 Architecture

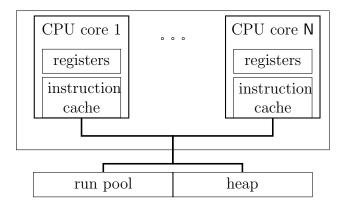

MIL envisages an abstract multi-processor with a shared main memory. Each processor consists of registers and of an instruction cache. The main memory is divided into a heap (for storing data and code blocks) and a run pool. Data blocks are represented by tuples and are protected by locks. Code blocks declare the needed registers (including the type for each register), the required locks, and an instruction set. The run pool contains suspended threads waiting for execution. It may happen that there are more threads to be run than the number of processors. Figure 3.1 summarizes the MIL architecture.

Figure 3.1: The MIL architecture.

### 3.2 Syntax

The syntax of our language is generated by the grammar in Figures 3.2, 3.3, and 3.9. We postpone the exposure of types to Section 3.4. We rely on a set of *heap labels* ranged over by l, and a disjoint set of *type variables* ranged over by  $\alpha$  and  $\beta$ .

Most of the proposed instructions, represented in Figure 3.2, are standard in assembly languages. Instructions are organised in sequences, ending in a jump or in a yield. Instruction yield frees the processor to execute another thread from the thread pool. Our threads are cooperative, meaning that each thread must explicitly release the processor (using the yield instruction).

The *abstract machine*, depicted in Figure 3.3, is parametric in the number of processors available (N) and in the number of registers (R).

An abstract machine can be in two possible states: halted or running. A running machine comprises a heap, a thread pool, and an array of processors. Heaps are maps from labels into *heap values* that may be tuples or code blocks. *Tuples* are vectors of values protected by some lock. Code blocks comprise a signature and a body. The signature of a code block describes the type of each register used in the body, and the locks held by the processor when jumping to the code block. The body is a sequence of instructions to be executed by a processor.

```

r ::= \mathsf{r}_1 \mid \ldots \mid \mathsf{r}_\mathsf{R}

registers

n ::= \ldots \mid -1 \mid 0 \mid 1 \mid \ldots

integer values

b ::= -1 | 0 | 1 | \dots

lock values

v ::= r \mid n \mid b \mid l \mid \mathsf{pack}\ \tau, v \mathsf{ as } \tau \mid \mathsf{packL}\ \alpha, v \mathsf{ as } \tau \mid

values

v[\tau] \mid ?\tau

instructions

\iota ::=

r:=v \ \mid \ r:=r+v \ \mid \ \text{if} \ r=v \ \text{jump} \ v \ \mid

control flow

r := \mathsf{malloc} \ [\vec{\tau}] \ \mathsf{guarded} \ \mathsf{by} \ \alpha \ |

memory

r := v[n] \mid r[n] := v \mid

\alpha, r := \mathsf{unpack}\ v

unpack

lock

\alpha, r := \mathsf{newLock}\ b \mid \alpha := \mathsf{newLockLinear}

r := \mathsf{tslE}\ v \mid r := \mathsf{tslS}\ v \mid \mathsf{unlockE}\ v \mid \mathsf{unlockS}\ v \mid

fork

fork v

I ::= \iota; I \mid \mathsf{jump} \ v \mid \mathsf{yield}

inst. sequences

```

Figure 3.2: Instructions

A thread pool is a multiset of pairs, each of which contains a pointer (i.e. a label) to a code block and a register file. A processor array contains N processors, where each is composed of a register file, a set of locks, and a sequence of instructions.

#### 3.3 Operational Semantics

Thread pools are managed by the rules illustrated in Figure 3.4. Rule R-HALT stops the machine when it finds an empty thread pool and, at the same time, all processors are idle, changing the machine state to halt. Otherwise, if there is an idle processor and a thread waiting in the pool, then by Rule R-SCHEDULE the thread is assigned to the idle processor. Rule R-FORK places a new thread in the pool, taking the ownership of locks required by

```

states

S ::= \langle H; T; P \rangle \mid \mathsf{halt}

H ::= \{l_1: h_1, \ldots, l_n: h_n\}

heaps

h ::= \langle v_1 \dots v_n \rangle^{\alpha} \mid \tau\{I\}

heap values

T ::= \{\langle l_1, R_1 \rangle, \dots, \langle l_n, R_n \rangle\}

thread pool

P ::= \{1: p_1, \dots, N: p_N\}

processors array

processor

p ::= \langle R; \Lambda; I \rangle

R ::= \{ \mathsf{r}_1 \colon v_1, \dots, \mathsf{r}_{\mathsf{R}} \colon v_{\mathsf{R}} \}

register files

\Lambda ::= (\lambda, \lambda, \lambda)

permissions

\lambda ::= \alpha_1, \ldots, \alpha_n

lock sets

```

Figure 3.3: Abstract machine

the forked code block.

Operational semantics regarding locks are depicted in Figure 3.5 and in Figure 3.6. The instruction newLock creates a new lock in three possible states, according to its parameter: locked exclusively (when the parameter is -1), locked shared (when the parameter is 1), and unlocked (when the parameter is 0). The scope of  $\alpha$  is the rest of the code block. A tuple with the value of the parameter of the newLock is allocated in the heap and register r is made to point it. For example, a new lock in the unlocked state allocates the tuple  $\langle \mathbf{0} \rangle^{\beta}$ . When the lock is created in the exclusive lock state, the new lock variable  $\beta$  is added to the set of exclusive locks held by the processor. Similarly, when the lock is created in the shared lock state, the new lock variable  $\beta$  is added to the set of shared locks held by the processor, allowing just one reader.

Linear locks are created by newLockLinear. The new lock variable  $\beta$  is added to the set of linear locks.

The Test and Set Lock, presented in many machines designed with multiple processes in mind, is an atomic operation that loads the contents of a word into a register and then stores another value in that word. There are two variations of the Test and Set Lock in our language: tslE and tslS. When a tslE is applied to an unlocked state, the type variable  $\alpha$  is added to the set of exclusive locks and the value becomes  $\langle -1 \rangle^{\alpha}$ . Various threads may

$$\frac{\forall i.P(i) = \langle .; .; \mathsf{yield} \rangle}{\langle .; \emptyset; P \rangle \to \mathsf{halt}} \tag{R-halt})}{\langle L(l) = \forall [.]\_ \mathsf{requires} \ \Lambda\{I\}} \\ \frac{H(l) = \forall [.]\_ \mathsf{requires} \ \Lambda\{I\}}{\langle H; T \uplus \{\langle l, R \rangle\}; P\{i \colon \langle .; .; \mathsf{yield} \rangle\} \rangle \to \langle H; T; P\{i \colon \langle R; \Lambda; I \rangle\} \rangle}{(\mathsf{R-SCHEDULE})} \\ \frac{\hat{\mathsf{R}}(v) = l \qquad H(l) = \forall [.]\_ \mathsf{requires} \ \Lambda\{.\}}{\langle H; T; \{i \colon \langle R; \Lambda \uplus \Lambda'; (\mathsf{fork} \ v; I) \rangle\} \rangle \to \langle H; T \cup \{\langle l, R \rangle\}; P\{i \colon \langle R; \Lambda'; I \rangle\} \rangle} \\ (\mathsf{R-FORK})}$$

Figure 3.4: Operational semantics (thread pool)

read values from a tuple locked in shared state, hence when  $\mathsf{tslS}$  is applied to a shared or to an unlocked lock the value contained in the tuple representing the lock is incremented, reflecting the number of readers holding the shared lock, and then the type variable  $\alpha$  is added to the set of hold shared locks. When  $\mathsf{tslS}$  is applied to a lock in the exclusive state, it places a -1 in the target register and the lock is not acquired by the thread issuing the operation.

Shared locks are unlocked with unlockS and the number of readers is decremented. The running processor must hold the shared lock. Exclusive locks are unlocked with unlockE, while the running processor holds the exclusive lock.

Rules related to memory instructions are illustrated in Figure 3.7. Values can be stored in a tuple, when the lock that guards the tuple is hold by the processor in the set of exclusive locks or in the set of linear locks. A value can be loaded from a tuple if the lock guarded by it is hold by the processor in any set of locks. The rule for malloc allocates a new tuple in the heap and makes r point to it. The size of the tuple is that of sequence of types  $[\vec{\tau}]$ , its values are uninitialised values.

The transition rules for the control flow instructions, illustrated in Figure 3.8, are straightforward [20]. They rely on function  $\hat{R}$  that works on registers or on values, by looking for values in registers, in packs, and in universal concretions.

Figure 3.5: Operational semantics (lock creation)

$$\hat{\mathbf{R}}(v) = \begin{cases} R(v) & \text{if } v \text{ is a register} \\ \mathsf{pack} \ \tau, \hat{\mathbf{R}}(v') \text{ as } \tau' & \text{if } v \text{ is pack } \tau, v' \text{ as } \tau' \\ \mathsf{packL} \ \alpha, \hat{\mathbf{R}}(v') \text{ as } \tau & \text{if } v \text{ is packL } \alpha, v' \text{ as } \tau \\ \hat{\mathbf{R}}(v')[\tau] & \text{if } v \text{ is } v'[\tau] \\ v & \text{otherwise} \end{cases}$$

#### 3.4 Type Discipline

The syntax of types is exposed in Figure 3.9. A type of the form  $\langle \vec{\sigma} \rangle^{\alpha}$  describes a tuple that is protected by lock  $\alpha$ . Each type  $\vec{\sigma}$  is either initialised ( $\tau$ ) or uninitialised (? $\tau$ ). A type of form  $\forall [\vec{\alpha}]\Gamma$  requires  $\Lambda$  describes a code block; a thread jumping into such a block must instantiate all the universal variables  $\vec{\alpha}$ ; it must also hold a register file type  $\Gamma$  as well as the locks in  $\Lambda$ . The singleton lock type, lock( $\alpha$ ), is used to represent the type of a lock value in the heap. The types  $\exists \alpha.\tau$  defines conventional existential type. With type  $\exists^{L}\alpha.\tau$  we are able to use the existential quantification over lock types, by following [4]. The recursive type, where the type may itself be present in the

$$\begin{split} & \underbrace{P(i) = \langle R; \Lambda; (r := \operatorname{tslS} v; I) \rangle}_{\langle H; T; P \rangle \to \langle H \{l \colon \langle b + \mathbf{1} \rangle^{\alpha} \}; T; P \{i \colon \langle R \{r \colon \mathbf{0} \}; (\lambda_E, \lambda_S \uplus \{\alpha\}, \lambda_L); I \rangle \} \rangle}_{\quad \text{(R-TSLS-ACQ)}} \\ & \underbrace{\frac{P(i) = \langle R; \Lambda; (r := \operatorname{tslS} v; I) \rangle}_{\langle H; T; P \rangle \to \langle H; T; P \{i \colon \langle R \{r \colon -\mathbf{1} \}; \Lambda; I \rangle \} \rangle}_{\quad \text{(R-TSLS-FAIL)}}}_{\quad \text{(R-TSLS-FAIL)}} \\ & \underbrace{\frac{P(i) = \langle R; \Lambda; (r := \operatorname{tslE} v; I) \rangle}_{\langle H; T; P \rangle \to \langle H; T; P \{i \colon \langle R \{r \colon \mathbf{0} \}; (\lambda_E \uplus \{\alpha\}, \lambda_S, \lambda_L); I \rangle \} \rangle}_{\quad \text{(R-TSLE-ACQ)}} \\ & \underbrace{\frac{P(i) = \langle R; \Lambda; (r := \operatorname{tslE} v; I) \rangle}_{\langle H; T; P \rangle \to \langle H \{l \colon \langle -\mathbf{1} \rangle^{\alpha} \}; T; P \{i \colon \langle R \{r \colon \mathbf{0} \}; (\lambda_E \uplus \{\alpha\}, \lambda_S, \lambda_L); I \rangle \} \rangle}_{\quad \text{(R-TSLE-FAIL)}} \\ & \underbrace{\frac{P(i) = \langle R; \Lambda; (r := \operatorname{tslE} v; I) \rangle}_{\langle H; T; P \rangle \to \langle H; T; P \{i \colon \langle R \{r \colon b \}; \Lambda; I \rangle \} \rangle}_{\quad \text{(R-TSLE-FAIL)}}}_{\quad \text{(R-UNLOCKS)}} \\ & \underbrace{\frac{P(i) = \langle R; (\lambda_E, \lambda_S \uplus \{\alpha\}, \lambda_L); (\operatorname{unlockS} v; I) \rangle}_{\langle H; T; P \rangle \to \langle H \{l \colon \langle \mathbf{0} \rangle^{\alpha} \}; T; P \{i \colon \langle R; (\lambda_E, \lambda_S, \lambda_L); I \rangle \} \rangle}_{\quad \text{(R-UNLOCKE)}} \\ & \underbrace{\frac{P(i) = \langle R; (\lambda_E \uplus \{\alpha\}, \lambda_S, \lambda_L); (\operatorname{unlockE} v; I) \rangle}_{\langle H; T; P \rangle \to \langle H \{l \colon \langle \mathbf{0} \rangle^{\alpha} \}; T; P \{i \colon \langle R; (\lambda_E, \lambda_S, \lambda_L); I \rangle \} \rangle}_{\quad \text{(R-UNLOCKE)}} \end{aligned}}$$

Figure 3.6: Operational semantics (lock manipulation)

types it is composed by, is defined by  $\mu\alpha.\tau$ .

The type system is presented in Figures 3.10 to 3.15. Typing for values is illustrated in Figure 3.10. Heap values are distinguished from operands (that include registers as well) by the form of the sequent. Uninitialised value  $?\tau$  has type  $?\tau$ ; we use the same syntax for a uninitialised value (at the left of the colon) and its type (at the right of the colon). A formula  $\sigma <: \sigma'$  allows to "forget" initialisations.

Instructions are checked against a typing environment  $\Psi$  (mapping labels to types, and type variables to the kind Lock: the kind of singleton lock types), a register file type  $\Gamma$  holding the current types of the registers, and

$$\frac{P(i) = \langle R; \Lambda; (r := \text{malloc } [\vec{\tau}] \text{ guarded by } \alpha; I) \rangle \qquad l \not\in \text{dom}(H)}{\langle H; T; P \rangle \rightarrow \langle H\{l \colon \langle \vec{?\tau} \rangle^{\alpha}\}; T; P\{i \colon \langle R\{r \colon l\}; \Lambda; I \rangle \} \rangle} \tag{R-MALLOC}}$$

$$\frac{P(i) = \langle R; \Lambda; (r := v[n]; I) \rangle \qquad H(\hat{\mathbf{R}}(v)) = \langle v_1..v_n..v_{n+m} \rangle^{\alpha}}{\langle H; T; P \rangle \rightarrow \langle H; T; P\{i \colon \langle R\{r \colon v_n\}; \Lambda; I \rangle \} \rangle} \qquad (\text{R-LOAD})}{\langle H; T; P \rangle \rightarrow \langle H\{l \colon \langle v_1...\hat{\mathbf{R}}(v)...v_{n+m} \rangle^{\alpha}\}} \qquad (\mathbf{R-HOAD})}$$

$$\frac{P(i) = \langle R; \Lambda; (r[n] := v; I) \rangle}{\langle H; T; P \rangle \rightarrow \langle H\{l \colon \langle v_1...\hat{\mathbf{R}}(v)...v_{n+m} \rangle^{\alpha}\}; T; P\{i \colon \langle R; \Lambda; I \rangle \} \rangle} \qquad (\mathbf{R-STORE})}$$

Figure 3.7: Operational semantics (memory)

a triple  $\Lambda$  that comprises sets of lock variables (the *permission* of the code block), that are, respectively, the exclusive, the shared, and the linear.

Rule T-YIELD requires that shared and exclusive locks must have been released prior to the ending of the thread. Rule T-FORK splits the permission into the two tuples  $\Lambda$  and  $\Lambda'$ : the former is transferred to the forked thread, the latter remains with the current thread, according to the permissions required by the target code block.

Rules T-New-lock1, T-New-lock-1, and T-New-lockL each adds the type variable into the respective set of locks. Rules T-New-lock0, T-New-lock1, and T-New-lock-1 assign a lock type to the register. Rules T-TSLE and T-TSLS require that the value under test holds a lock, disallowing testing a lock already held by the thread. Rules T-unlockE and T-unlockS make sure that only held locks are unlocked. Finally, the rules T-Criticale and T-Criticals ensure that the current thread holds the exact number of locks required by the target code block. Each of these rules also adds the lock under test to the respective set of locks of the thread. A thread is guaranteed to hold the lock only after (conditionally) jumping to a critical region. A previous test and set lock instructions may have obtained the lock, but as far as the type system goes, the thread holds the lock after the conditional jump.

The typing rules for memory and control flow are depicted in Figure 3.13 and Figure 3.14. The rule for malloc ensures that allocated memory is pro-

$$\frac{P(i) = \langle R; \Lambda; \mathsf{jump} \ v \rangle \qquad H(\hat{\mathbf{R}}(v)) = \_\{I\}}{\langle H; T; P \rangle \rightarrow \langle H; T; P \{i \colon \langle R; \Lambda; I \rangle \} \rangle} \qquad \qquad (\text{R-Jump})$$

$$\frac{P(i) = \langle R; \Lambda; (r := v; I) \rangle}{\langle H; T; P \rangle \rightarrow \langle H; T; P \{i \colon \langle R \{r \colon \hat{\mathbf{R}}(v) \}; \Lambda; I \rangle \} \rangle} \qquad \qquad (\text{R-MOVE})$$

$$\frac{P(i) = \langle R; \Lambda; (r := r' + v; I) \rangle}{\langle H; T; P \rangle \rightarrow \langle H; T; P \{i \colon \langle R \{r \colon R(r') + \hat{\mathbf{R}}(v) \}; \Lambda; I \rangle \} \rangle} \qquad \qquad (\text{R-ARITH})$$

$$P(i) = \langle R; \Lambda; (\text{if} \ r = v \ \text{jump} \ v'; \bot) \rangle$$

$$\frac{R(r) = v \qquad H(\hat{\mathbf{R}}(v')) = \_\{I\}}{\langle H; T; P \rangle \rightarrow \langle H; T; P \{i \colon \langle R; \Lambda; I \rangle \} \rangle} \qquad \qquad (\text{R-BRANCHT})$$

$$\frac{P(i) = \langle R; \Lambda; (\text{if} \ r = v \ \text{jump} \ \bot; I) \rangle \qquad R(r) \neq v}{\langle H; T; P \rangle \rightarrow \langle H; T; \{i \colon \langle R; \Lambda; I \rangle \} \rangle} \qquad \qquad (\text{R-BRANCHF})$$

$$\frac{P(i) = \langle R; \Lambda; (\alpha, r := \text{unpack} \ v; I) \rangle \qquad \hat{\mathbf{R}}(v) = \text{pack} \ \tau, v' \ \text{as} \ \_}{\langle H; T; P \rangle \rightarrow \langle H; T; P \{i \colon \langle R \{r \colon v' \}; \Lambda; I[\tau/\alpha] \rangle \} \rangle} \qquad \qquad (\text{R-UNPACK})$$

$$\frac{P(i) = \langle R; \Lambda; (\alpha, r := \text{unpack} \ v; I) \rangle \qquad \hat{\mathbf{R}}(v) = \text{pack} \ \mathcal{L} \beta, v' \ \text{as} \ \_}{\langle H; T; P \rangle \rightarrow \langle H; T; P \{i \colon \langle R \{r \colon v' \}; \Lambda; I[\beta/\alpha] \rangle \} \rangle} \qquad \qquad (\text{R-UNPACKL})$$

Figure 3.8: Operational semantics (control flow)

tected by a lock  $(\alpha)$  present in the scope. The lock that guards a tuple defines the permissions that affect how the loading and the storing operations work. Holding a lock of any kind enables permission to load a value from a tuple. Only exclusive and linear locks permit storing a value into a tuple.

The rules for typing machine states are illustrated in Figure 3.15. They should be easy to follow. The only remark goes to heap tuples, where we make sure that all locks protecting the tuples are in the domain of the typing environment.

Figure 3.9: Types

### 3.5 Examples

We select a case in point of inter-process communication: mutual exclusion. We create a tuple and then start two threads that try to write in the tuple concurrently. A reference for lock  $\alpha$  is transferred to each new thread, by instantiating the universal value, since it is not in the scope of the forked threads.

```

\begin{aligned} & \text{main()} \ \{ \\ & \alpha, \ r_1 := \text{newLock} \ -1 \\ & r_2 := \text{malloc} \ [\text{int}] \ \text{guarded by} \ \alpha \\ & r_2[0] := 0 \\ & \text{unlockE} \ r_1 \\ & \text{fork} \ \text{thread1}[\alpha] \\ & \text{fork thread2}[\alpha] \\ & \text{yield} \end{aligned}

```

Each thread competes in acquiring lock  $\alpha$  using different strategies. In the first thread (thread1) we use a technique called *spin lock*, where we loop actively, not releasing the processor, until we eventually grab the lock exclusively. After that we jump to the critical region.

```

thread1 \forall [\alpha](r_1: \langle \mathbf{lock}(\alpha) \rangle^{\alpha}, r_2: \langle ? \mathsf{int} \rangle^{\alpha}) { r_3:= tslE r_1-- exclusive because we want to write if r_3= 0 jump criticalRegion [\alpha] jump thread1[\alpha] }

```

$$\vdash \langle \sigma_{1}, \dots, \tau_{n}, \dots, \sigma_{n+m} \rangle^{\alpha} <: \langle \sigma_{1}, \dots, ?\tau_{n}, \dots, \sigma_{n+m} \rangle^{\alpha} \qquad (S-\text{UNINIT})$$

$$\frac{n \leq m}{\vdash \mathsf{r}_{0} \colon \tau_{0}, \dots, \mathsf{r}_{m} \colon \tau_{m} <: \mathsf{r}_{0} \colon \tau_{0}, \dots, \mathsf{r}_{n} \colon \tau_{n}} \qquad (S-\text{REG-FILE})$$

$$\vdash \sigma <: \sigma \qquad \frac{\vdash \sigma <: \sigma' \qquad \vdash \sigma' <: \sigma''}{\vdash \sigma <: \sigma''} \qquad (S-\text{REF, S-TRANS})$$

$$\frac{\vdash \tau' <: \tau}{\Psi, l \colon \tau' \vdash l \colon \tau} \qquad \Psi \vdash n \colon \text{int} \qquad \Psi \vdash b \colon \mathsf{lock}(\alpha) \qquad \Psi \vdash ?\tau \colon ?\tau$$

$$\frac{(T-\text{LABEL, T-INT, T-LOCK, T-UNINIT})}{\Psi \vdash \mathsf{v} \colon \tau'[\tau/\alpha] \qquad \alpha \notin \tau, \Psi} \qquad \frac{\Psi \vdash v \colon \tau[\beta/\alpha] \qquad \alpha \notin \beta, \Psi}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau \colon \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau \colon \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau \colon \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau \colon \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau \colon \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau \colon \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau \colon \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau \colon \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau \colon \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau \colon \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau \colon \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau \colon \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau}$$

$$\frac{\Psi \vdash v \colon \tau}{\Psi \vdash \mathsf{packL} \ \beta, v \ \text{as} \ \exists^{\mathsf{L}} \alpha. \tau}$$

Figure 3.10: Typing rules for values  $\Psi \vdash v : \sigma$  and for operands  $\Psi ; \Gamma \vdash v : \sigma$

In the critical region, the value contained in the tuple is incremented.

```

criticalRegion \forall [\alpha](r_1: \langle \mathbf{lock}(\alpha) \rangle^{\alpha}, r_2: \langle ?\mathsf{int} \rangle^{\alpha}) requires(\alpha;;) { r_3:=r_2[0] r_3:=r_3+1 r_2[0]:=r_3 unlockE r_1 yield }

```

In the second thread (thread2), we opt for a different technique called *sleep lock*. This strategy is cooperative towards other threads, since the control of the processor is not held exclusively until the lock's permission is granted. We try to acquire the lock exclusively. When we do, we jump to the critical region. If we do not acquire the lock, we fork a copy of this thread that will try again later.

```

thread2 \forall [\alpha](r_1: \langle \mathbf{lock}(\alpha) \rangle^{\alpha}, r_2: \langle \mathsf{int} \rangle^{\alpha}) \{

r_3:=\mathbf{tslE} \ r_1-- \ exclusive \ because \ we \ want \ to \ write

```

$$\begin{split} \Psi; \Gamma; (\emptyset, \emptyset, \lambda_L) &\vdash \mathsf{yield} & (\text{T-YIELD}) \\ \frac{\Psi; \Gamma \vdash v \colon \forall []\Gamma' \text{ requires } \Lambda \quad \Psi; \Gamma; \Lambda' \vdash I \quad \vdash \Gamma <\colon \Gamma'}{\Psi; \Gamma; \Lambda \uplus \Lambda' \vdash \text{ fork } v; I} \\ \frac{\Psi, \alpha \colon \mathsf{Lock}; \Gamma\{r \colon \langle \mathsf{lock}(\alpha) \rangle^{\alpha}\}; \Lambda \vdash I \quad \alpha \not\in \Psi, \Gamma, \Lambda}{\Psi; \Gamma; \Lambda \vdash \alpha, r \coloneqq \mathsf{newLock } \mathbf{0}; I} \\ \frac{\Psi, \alpha \colon \mathsf{Lock}; \Gamma\{r \colon \langle \mathsf{lock}(\alpha) \rangle^{\alpha}\}; (\lambda_E, \lambda_S \uplus \{\alpha\}, \lambda_L) \vdash I \quad \alpha \not\in \Psi, \Gamma, \Lambda}{\Psi; \Gamma; \Lambda \vdash \alpha, r \coloneqq \mathsf{newLock } \mathbf{1}; I} \\ \frac{\Psi, \alpha \colon \mathsf{Lock}; \Gamma\{r \colon \langle \mathsf{lock}(\alpha) \rangle^{\alpha}\}; (\lambda_E \uplus \{\alpha\}, \lambda_S, \lambda_L) \vdash I \quad \alpha \not\in \Psi, \Gamma, \Lambda}{\Psi; \Gamma; \Lambda \vdash \alpha, r \coloneqq \mathsf{newLock } \mathbf{-1}; I} \\ \frac{\Psi, \alpha \colon \mathsf{Lock}; \Gamma\{r \colon \langle \mathsf{lock}(\alpha) \rangle^{\alpha}\}; (\lambda_E \uplus \{\alpha\}, \lambda_S, \lambda_L) \vdash I \quad \alpha \not\in \Psi, \Gamma, \Lambda}{\Psi; \Gamma; \Lambda \vdash \alpha, r \coloneqq \mathsf{newLock } \mathbf{-1}; I} \\ \frac{\Psi, \alpha \colon \mathsf{Lock}; \Gamma; (\lambda_E, \lambda_S, \lambda_L \uplus \{\alpha\}) \vdash I \quad \alpha \not\in \Psi, \Gamma, \Lambda}{\Psi; \Gamma; \Lambda \vdash \alpha \coloneqq \mathsf{newLockLinear}; I} \\ (\text{T-NEW-LOCK } \mathbf{-1}) \\ \frac{\Psi, \alpha \colon \mathsf{Lock}; \Gamma; (\lambda_E, \lambda_S, \lambda_L \uplus \{\alpha\}) \vdash I \quad \alpha \not\in \Psi, \Gamma, \Lambda}{\Psi; \Gamma; \Lambda \vdash \alpha \coloneqq \mathsf{newLockLinear}; I} \\ (\text{T-NEW-LOCKL}) \end{aligned}$$

Figure 3.11: Typing rules for instructions (thread pool and lock creation)  $\Psi; \Gamma; \Lambda \vdash I$

```

\begin{array}{ll} \textbf{if} & r_3 = 0 \ \textbf{jump} \ \text{criticalRegion} \left[\alpha\right] \\ \textbf{fork} & \text{thread2} \left[\alpha\right] \\ \textbf{yield} \\ \end{array} \}

```

These two techniques have advantages over each other. A spin lock is faster. A sleep lock is fairest to other threads. When there is a reasonable expectation that the lock will be available (with exclusive access) in a short period of time it is more appropriate to use a spin lock. The sleep lock technique, however, does context switching, which is an expensive operation (*i.e.* degrades performance). A short coming of the spin lock in machines with only one processor is demonstrated in this example:

```

\label{eq:main} \begin{array}{l} \text{main () } \{ \\ \alpha, \ r_1 := \ \mathsf{newLock} \ -1 \\ \text{ fork } \ \mathsf{release} \ [\alpha] \\ \text{ jump } \ \mathsf{spinLock}[\alpha] \\ \} \\ \mathsf{release} \ \ \forall [\alpha] \ \ (r_1 : \ \langle \mathsf{lock}(\alpha) \rangle^\alpha) \ \ \mathsf{requires} \ \ (\alpha;;) \ \ \{ \ \ \mathsf{lock}(\alpha) \rangle^\alpha \} \\ \end{array}

```

$$\frac{\Psi;\Gamma\vdash v\colon\langle \mathsf{lock}(\alpha)\rangle^{\alpha} \quad \Psi;\Gamma\{r\colon \mathsf{lockS}(\alpha)\};\Lambda\vdash I \quad \alpha\not\in\Lambda}{\Psi;\Gamma;\Lambda\vdash r:=\mathsf{tslS}\ v;I} \qquad (\text{T-TSLS})$$

$$\frac{\Psi;\Gamma\vdash v\colon\langle \mathsf{lock}(\alpha)\rangle^{\alpha} \quad \Psi;\Gamma\{r\colon \mathsf{lockE}(\alpha)\};\Lambda\vdash I \quad \alpha\not\in\Lambda}{\Psi;\Gamma;\Lambda\vdash r:=\mathsf{tslE}\ v;I} \qquad (\text{T-TSLE})$$

$$\frac{\Psi;\Gamma\vdash v\colon\langle \mathsf{lock}(\alpha)\rangle^{\alpha} \quad \alpha\in\lambda_{S} \quad \Psi;\Gamma;(\lambda_{S}\setminus\{\alpha\},\lambda_{E},\lambda_{L})\vdash I}{\Psi;\Gamma;(\lambda_{S},\lambda_{E},\lambda_{L})\vdash \mathsf{unlockS}\ v;I} \qquad (\text{T-UNLOCKS})$$

$$\frac{\Psi;\Gamma\vdash v\colon\langle \mathsf{lock}(\alpha)\rangle^{\alpha} \quad \alpha\in\lambda_{E} \quad \Psi;\Gamma;(\lambda_{S},\lambda_{E}\setminus\{\alpha\},\lambda_{L})\vdash I}{\Psi;\Gamma;(\lambda_{S},\lambda_{E},\lambda_{L})\vdash \mathsf{unlockE}\ v;I} \qquad (\text{T-UNLOCKE})$$

$$\frac{\Psi;\Gamma\vdash r\colon \mathsf{lockS}(\alpha)\quad \Psi;\Gamma\vdash v\colon\forall[\Gamma'\ \mathsf{requires}\ (\lambda_{E},\lambda_{S}\uplus\{\alpha\},\lambda_{L}')}{\Psi;\Gamma;\Lambda\vdash I \qquad \vdash\Gamma<\colon\Gamma' \quad \lambda_{L}'\subseteq\lambda_{L}} \qquad (\text{T-CRITICALS})$$

$$\frac{\Psi;\Gamma\vdash r\colon \mathsf{lockE}(\alpha)\quad \Psi;\Gamma\vdash v\colon\forall[\Gamma'\ \mathsf{requires}\ (\lambda_{E}\uplus\{\alpha\},\lambda_{S},\lambda_{L}')}{\Psi;\Gamma;\Lambda\vdash I \qquad \vdash\Gamma<\colon\Gamma' \quad \lambda_{L}'\subseteq\lambda_{L}} \qquad (\text{T-CRITICALE})$$

Figure 3.12: Typing rules for instructions (locks)  $\Psi$ ;  $\Gamma$ ;  $\Lambda \vdash I$

```

\begin{array}{l} \textbf{unlockE} \ r_1 \\ \textbf{yield} \\ \\ \\ \text{spinLock} \ \forall [\alpha] \ \left( r_1 : \langle \textbf{lock}(\alpha) \rangle^{\alpha} \right) \left\{ \\ r_2 := \ \textbf{tslE} \ r_1 \\ \textbf{if} \ r_2 = 0 \\ \textbf{jump} \ \text{someComputation}[\alpha] \ -- \ \textit{will never happen} \\ \textbf{jump} \ \text{spinLock}[\alpha] \\ \\ \\ \\ \\ \\ \\ \\ \\ \end{array} \right\}

```

The permission of lock  $\alpha$  is given to the forked process that will execute the code block release — when a processor is available. Afterwards, a spin lock is performed to obtain lock  $\alpha$ . But because the sole processor is busy trying to acquire lock  $\alpha$ , the scheduled thread that can release it will never

$$\frac{\Psi,\alpha\colon \mathsf{Lock}; \Gamma\{r\colon \langle\vec{?}\tau\rangle^\alpha\}; \Lambda\vdash I \qquad \vec{\tau} \neq \mathsf{lock}(\_), \mathsf{lockS}(\_), \mathsf{lockE}(\_)}{\Psi,\alpha\colon \mathsf{Lock}; \Gamma; \Lambda\vdash r := \mathsf{malloc}} \ [\vec{\tau}] \ \mathsf{guarded} \ \mathsf{by} \ \alpha; I \qquad \qquad (\mathsf{T-MALLOC})$$

$$\frac{\Psi; \Gamma\vdash v\colon \langle\sigma_1..\tau_n..\sigma_{n+m}\rangle^\alpha \quad \Psi; \Gamma\{r\colon \tau_n\}; \Lambda\vdash I \quad \tau_n \neq \mathsf{lock}(\_) \quad \alpha\in \Lambda}{\Psi; \Gamma; \Lambda\vdash r := v[n]; I} \qquad \qquad (\mathsf{T-LOAD})$$

$$\Psi; \Gamma\vdash v\colon \tau_n \quad \Psi; \Gamma\vdash r\colon \langle\sigma_1..\sigma_n..\sigma_{n+m}\rangle^\alpha \quad \tau_n \neq \mathsf{lock}(\_)$$

$$\Psi; \Gamma\{r\colon \langle\sigma_1.. \operatorname{type}(\sigma_n)..\sigma_{n+m}\rangle^\alpha\}; \Lambda\vdash I \quad \alpha\in \lambda_E\cup \lambda_L \qquad (\mathsf{T-STORE})$$

$$\frac{\Psi; \Gamma\vdash v\colon \tau \quad \Psi; \Gamma\{n\} := v; I}{\Psi; \Gamma\vdash v\colon \mathsf{int} \quad \Psi; \Gamma\vdash v\colon \mathsf{int} \quad \Psi; \Gamma\vdash v\colon \mathsf{int} \}; \Lambda\vdash I} \qquad (\mathsf{T-MOVE})$$

$$\frac{\Psi; \Gamma\vdash r'\colon \mathsf{int} \quad \Psi; \Gamma\vdash v\colon \mathsf{int} \quad \Psi; \Gamma\vdash v\colon \mathsf{int} \}; \Lambda\vdash I}{\Psi; \Gamma; \Lambda\vdash r:= r'+v; I} \qquad (\mathsf{T-ARITH})$$

where  $type(\tau) = type(?\tau) = \tau$ .

Figure 3.13: Typing rules for instructions (memory)  $\Psi$ ;  $\Gamma$ ;  $\Lambda \vdash I$

be executed.

The continuation passing style [7] suits programs written in MIL, since they are executed by a stack-less machine. In this programming model the user passes a continuation (a label) to a code block that proceeds in the continuation label after it is executed (either by forking or by jumping). It may be useful to pass user data to the continuation code (as one of its parameters). Existential types enable abstracting the type of the user data. Let UserContinuation stands for

$$\forall [\alpha](r_1:\langle ?\mathsf{int}\rangle^\alpha) \text{ requires } (;;\alpha)$$

Let PackedUserData stands for

$$\exists \beta. \langle \forall [\gamma](r_1:\beta) \text{ requires } (;;\gamma), \beta \rangle^{\alpha}$$

The type PackedUserData is a pair that is divided into the continuation of type

$$\forall [\gamma](r_1:\beta) \text{ requires } (;;\gamma)$$

$$\frac{\Psi;\Gamma\vdash v\colon\exists\alpha.\tau\quad \Psi;\Gamma\{r\colon\tau\};\Lambda\vdash I\quad \alpha\not\in\Psi,\Gamma,\Lambda}{\Psi;\Gamma;\Lambda\vdash\alpha,r:=\text{unpack }v;I}\qquad \text{(T-unpack)}$$

$$\frac{\Psi;\Gamma\vdash v\colon\exists^{\text{L}}\alpha.\tau\quad \Psi,\beta\colon\text{Lock};\Gamma\{r\colon\tau\};\Lambda\vdash I\quad \alpha\not\in\Psi,\Gamma,\Lambda}{\Psi;\Gamma;\Lambda\vdash\alpha,r:=\text{unpack }v;I}$$

$$\frac{\Psi;\Gamma\vdash r\colon\text{int}\quad \Psi;\Gamma\vdash v\colon\forall[]\Gamma'\text{ requires }(\lambda_E,\lambda_S,\lambda_L')}{\Psi;\Gamma;\Lambda\vdash I\quad \vdash\Gamma<\colon\Gamma'\quad \lambda_L'\subseteq\lambda_L}\qquad \text{(T-unpackL)}$$

$$\frac{\Psi;\Gamma\vdash v\colon\forall[]\Gamma'\text{ requires }(\lambda_E,\lambda_S,\lambda_L')\quad \vdash\Gamma<\colon\Gamma'\quad \lambda_L'\subseteq\lambda_L}{\Psi;\Gamma;\Lambda\vdash\text{if }r=0\text{ jump }v;I}$$

$$\frac{\Psi;\Gamma\vdash v\colon\forall[]\Gamma'\text{ requires }(\lambda_E,\lambda_S,\lambda_L')\quad \vdash\Gamma<\colon\Gamma'\quad \lambda_L'\subseteq\lambda_L}{\Psi;\Gamma;\Lambda\vdash\text{jump }v} \qquad \text{(T-jump)}$$

where  $type(\tau) = type(?\tau) = \tau$ .

Figure 3.14: Typing rules for instructions (memory and control flow)  $\Psi; \Gamma; \Lambda \vdash I$

and the user data of type  $\beta$ , respectively. The type of the user data and the type of register  $r_1$ , present in the continuation, is the same.

The pattern of usage for a value of type PackedUSerData is to unpack the continuation and the user data, and "apply" the former to the latter — by moving the user data into register  $r_1$ , and then jumping to the continuation. The user data is an *opaque* value to the block of code manipulating the pair. The advantages of an opaque user data is twofold. Firstly, the user data is unaltered by the manipulator. Secondly, the code using the pair is not bound to the type of the user data.

Next is an example of how to make a call to a code block that uses the continuation passing style:

```

\begin{array}{l} \mathsf{main}() \ \{ \\ \alpha := \mathsf{newLockLinear} \\ r_2 := \mathsf{malloc}[\mathsf{int}] \ \mathsf{guarded} \ \mathsf{by} \ \alpha \\ r_1 := \mathsf{malloc}[\mathsf{ContinuationType}, \ \langle ?\mathsf{int} \rangle^\alpha] \ \mathsf{guarded} \ \mathsf{by} \ \alpha \\ r_1[0] := \mathsf{continuation} \\ r_1[1] := r_2 \\ r_1 := \mathsf{pack} \ r_1, \ \langle ?\mathsf{int} \rangle^\alpha \ \mathsf{as} \ \mathsf{PackedUserData} \\ \mathsf{jump} \ \mathsf{library} \ [\alpha] \end{array}

```

$$\frac{\forall i.\Psi \vdash R(r_i) \colon \Gamma(r_i)}{\Psi \vdash R \colon \Gamma} \qquad \qquad (\text{reg file, } \underline{\Psi \vdash R \colon \Gamma})$$

$$\frac{\forall i.\Psi \vdash P(i)}{\Psi \vdash P} \qquad \frac{\Psi \vdash R \colon \Gamma \quad \Psi ; \Gamma ; \Lambda \vdash I}{\Psi \vdash \langle R ; \Lambda ; I \rangle} \qquad (\text{processors, } \underline{\Psi \vdash P})$$

$$\frac{\forall i.\Psi \vdash l_i \colon \forall [\vec{\alpha}_i] \Gamma_i \text{ requires } -\{-\} \quad \Psi \vdash R_i \colon \Gamma_i [\vec{\beta}_i / \vec{\alpha}_i]}{\Psi \vdash \{\langle l_1, R_1 \rangle, \dots, \langle l_n, R_n \rangle\}} \qquad (\text{thread pool, } \underline{\Psi \vdash T})$$

$$\underline{\Psi, \vec{\alpha} \colon \mathsf{Lock}; \Gamma; \Lambda \vdash I} \qquad \qquad \forall i.\Psi, \alpha \colon \mathsf{Lock} \vdash v_i \colon \sigma_i} \qquad \forall i.\Psi, \alpha \colon \mathsf{Lock} \vdash v_i \colon \sigma_i} \qquad (\mathsf{heap value, } \underline{\Psi \vdash H})$$

$$\underline{\Psi \vdash H} \qquad \qquad (\mathsf{heap value, } \underline{\Psi \vdash H})$$

$$\vdash \mathsf{halt} \qquad \frac{\Psi \vdash H}{\Psi \vdash H} \qquad \Psi \vdash T \qquad \Psi \vdash P} \qquad (\mathsf{heap, } \underline{\Psi \vdash H})$$

$$\vdash \mathsf{halt} \qquad \qquad (\mathsf{state, } \vdash S)$$

Figure 3.15: Typing rules for machine states

```

\label{eq:continuation} \left\{ \begin{array}{l} \text{library } [\alpha](r_1: \mathsf{PackedUserData}) \ \mathbf{requires} \ (;;\alpha) \ \{\\ -- \ do \ some \ computation... \\ \times, \ r_1 := \ \mathbf{unpack} \ r_1 -- \ we \ do \ not \ need \ the \ packed \ type \ here \\ r_2 := r_1[0] \qquad -- \ the \ continuation \\ r_1 := r_1[1] \qquad -- \ the \ user \ data \\ \mathbf{jump} \ r_2[\alpha] \\ \} \\ \text{continuation } \text{ContinuationType} \ \{\\ -- \ do \ some \ work \\ \} \end{array}

```

The code block main allocates the user data of type  $\langle ?int \rangle^{\alpha}$ . Afterwards, the user data is stored into a tuple, along with the label pointing to the continuation. The tuple is then packed and passed to the library, which eventually calls the continuation by unpacking the packed data and jumping to the stored label.

## Chapter 4

## The $\pi$ -Calculus Run-time

In this chapter we describe a library, written in MIL, that implements the primitives of the  $\pi$ -calculus used to support the generated code, following the design of Lopes et al. [12].

We implement a message passing paradigm in a shared memory architecture. Because communication in the  $\pi$ -calculus version we select is asynchronous, the output process may be represented (in this run-time) by the message being transmitted itself, which is buffered until delivery in the representation of the transmitting channel. We also define a mechanism to schedule a process waiting for a message to be delivered, by blocking its execution, and then resuming it, when a message arrives. This mechanism is used to represent the input process and the replicated input process.

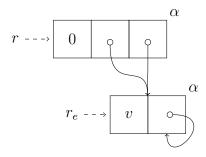

The closure of a process consists of an environment (the variables known by the process itself) and a continuation (a pointer to a code block that embodies the process). We store the closure of processes waiting for a message to be delivered in the target channel. When messages are delivered, we recover the state of the process — by applying the message and the environment into the continuation — and resume its execution.

We present a set of macros used to abstract the definition of types and of operations. For each introduced data structure, we define macros for describing its type, for allocating it, and for accessing the values that compose it. We build our library on top of queues defined in the Appendix A. On Section 4.1, we implement channels. Next we describe operations to send through, and to receive from, a channel. Lastly, we extend the definition of channels, associating a channel with its lock in a tuple (Section 4.3).

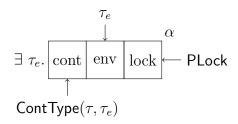

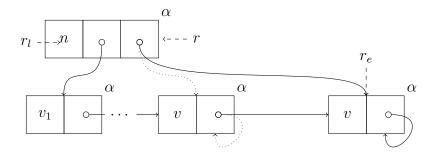

Figure 4.1: The closure of a process

#### 4.1 Channels Queues

In this section, we define the type of a process and the type of a channel queue. A *channel queue* is used for asynchronous message passing between processes, which consists of two pools, one for storing messages and another for storing processes. The continuation of a process is the code block that represents a process, expecting the message being delivered, the environment of the process, and a lock protecting the environment. A process is, therefore, composed by the continuation, the environment, and the environment's lock.

The continuation of a process may be defined by the parametrised type:

$$\mathsf{ContType}(\tau_m, \tau_e) \stackrel{\mathsf{def}}{=} [\alpha](r_1 : \tau_m, \ r_2 : \tau_e, \ r_3 : \langle \mathsf{lock}(\alpha) \rangle^{\alpha}) \ \mathsf{requires} \ (;\alpha;)$$

Register  $r_1$  (of type  $\tau_m$ ) holds the received message, register  $r_2$  holds the environment of the process (of type  $\tau_e$ ), and register  $r_3$  holds the lock (of type  $\langle \mathsf{lock}(\alpha) \rangle^{\alpha}$ ) that may protect the environment. Lock  $\alpha$  is abstracted by the universal operator. Notice that the code block only has permission to read values from the environment, because the environment of a process is a immutable structure, as can be observed in Chapter 5.

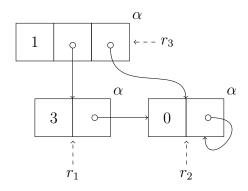

The type of the closure of a process, sketched by Figure 4.1, may be defined by:

ClosureType

$$(\tau,\alpha) \stackrel{\text{def}}{=} \exists \tau_e.\langle \text{ContType}(\tau,\tau_e), \tau_e, \text{PLock}() \rangle^{\alpha}$$

The existential value that abstracts the environment (of type  $\tau_e$ ) of the process (allowing environments of different types) holds a tuple that consists of the continuation, the environment, and the lock type that protects the environment. The continuation process is of type ContType( $\tau,\tau_e$ ), communicating messages of type  $\tau$  and holding an environment of type  $\tau_e$ . The lock of the environment is defined by:

Figure 4.2: A process

$$\mathsf{PLock}() \stackrel{\mathsf{def}}{=} \exists^{\mathsf{L}} \beta. \langle \mathsf{lock}(\beta) \rangle^{\beta}$$

and is an existential lock value abstracting lock  $\beta$ . Observe that we have extended the definition of closure, by adding the lock of the environment. This extension grants access to data stored inside the environment. The macros for handling closures are:

```

ClosureAlloc (\tau_m, \tau_e, \alpha) \stackrel{\text{def}}{=} \mathbf{malloc}[\mathsf{ContType}(\tau_m, \tau_e), \ \tau_e, \ \mathsf{PLock}()] guarded by \alpha ClosureCont(r) \stackrel{\text{def}}{=} r[0] ClosureEnv(r) \stackrel{\text{def}}{=} r[1] ClosureLock(r) \stackrel{\text{def}}{=} r[2]

```

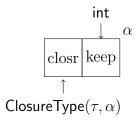

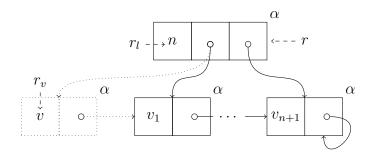

We may define a process (illustrated by Figure 4.2) as a pair containing the closure and the *keep in channel* flag (of type int):

$$\mathsf{ProcType}(\tau,\alpha) \ \stackrel{\mathsf{def}}{=} \ \langle \mathsf{ClosureType}(\tau,\alpha), \ \mathsf{int} \, \rangle^{\alpha}$$

The flag is necessary for replicated input processes: after reduction, these processes remain in the channel queue, waiting for more messages. Macros to manipulate processes are:

```

\begin{split} \operatorname{ProcAlloc}(\tau, \alpha) &\stackrel{\operatorname{def}}{=} \operatorname{malloc}[\operatorname{ClosureType}(\tau, \alpha), \operatorname{int}] \text{ guarded by } \alpha \\ \operatorname{ProcClosure}(r) &\stackrel{\operatorname{def}}{=} r[0] \\ \operatorname{ProcKeep}(r) &\stackrel{\operatorname{def}}{=} r[1] \end{split}

```

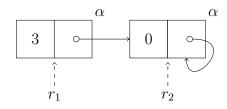

The creation of a process is illustrated in the following example, where c has type ContType(int, $\langle \rangle^{\beta}$ ) and  $r_1$  has type  $\langle \mathsf{lock}(\beta) \rangle^{\beta}$ :

```

r_3:= malloc [] guarded by eta —— an empty environment is created r_2:= ClosureAlloc(int, \langle \rangle^{eta}, lpha) —— alloc the closure of a process ClosureCont(r_2):= c —— set the continuation to 'c'

```

```

\begin{array}{lll} {\sf ClosureEnv}(r_2) := r_3 & -- \  \, \text{set the environment to the one in} \  \, r_3 \\ {\sf ClosureLock}(r_2) := r_1 & -- \  \, \text{set the lock of the environment as} \  \, \beta \\ r_2 := \  \, {\sf pack} \ \langle \rangle^\beta, \  \, r_2 \  \, {\sf as} \  \, {\sf ClosureType}(\mathsf{int}\,,\alpha) \, \, -- \  \, \text{abstract the environment's type} \\ r_1 := \  \, {\sf ProcAlloc}(\mathsf{int}\,,\alpha) & -- \  \, \text{alloc the process} \  \, \text{itself} \\ {\sf ProcClosure}(r_1) := r_2 & -- \  \, \text{set the closure as the one we created} \\ {\sf ProcKeep}(r_1) := 0 & -- \  \, \text{do not keep this process} \  \, \text{in the channel} \\ \end{array}

```

In order to create a queue of processes, we need to define a sentinel process. Consider sink:

```

sink [\alpha, \tau_m, \tau_e](r_1:\tau_m, r_2:\tau_e, r_3:\langle lock(\alpha)\rangle^{\alpha}) requires (;\alpha;) { unlockS r_3 yield }

```

Instantiating the universal value sink with  $\tau_m$  and  $\tau_e$  (sink  $[\tau_m][\tau_e]$ ) results in a value of type ContType $(\tau_e, \tau_m)$ . We may use this continuation in sentinel processes.

The creation of a sentinel process may be defined by macro ProcCreate-Sentinel $(r, r_t, \tau, \alpha)$ , where:

- r is the register that will refer the process of type  $ProcType(\tau,\alpha)$ ;

- $r_s$  is the register that will refer the closure of type ClosureType $(\tau,\alpha)$ ;

- $\tau$  is the type of the messages being transmitted;

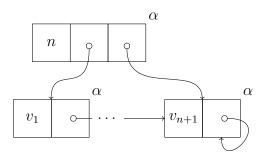

Channel queues (Figure 4.3) may be defined by:

•  $\alpha$  is the lock protecting the channel.

#### Defined by:

```

ProcCreateSentinel(r, r_s, \tau, \alpha) \stackrel{\text{def}}{=}

\delta, r := \text{newLock } 0

— create a dummy lock

r := \mathbf{packL} \ \delta, r \ \mathbf{as} \ \mathsf{PLock}()

— abstract the lock

r_s:= ClosureAlloc(\tau, int, \alpha)

— alloc the closure of the process

ClosureCont(r_s) := \text{sink}[\text{int }][\tau] — set the continuation to 'sink'

ClosureEnv(r_s) := 0

-- set value 0 as the environment

ClosureLock(r_s) := r

-- set the lock of the environment as r

r_s:= pack int, r_s as ClosureType(\tau, \alpha) — abstract the environment

r := \mathsf{ProcAlloc}(\tau, \alpha)

— alloc the sentinel process

ProcClosure(r) := r_s

-- set the closure as the one in r_s

ProcKeep(r) := 0

-- do not keep this process in the queue

```

Figure 4.3: A channel queue

ChannelQueueType

$$(\tau,\alpha) \stackrel{\text{def}}{=} \langle \text{int, QueueType}(\tau,\alpha), \text{QueueType}(\text{ProcType}(\tau,\alpha),\alpha) \rangle^{\alpha}$$

representing a tuple, protected by lock  $\alpha$ , that holds a flag (of type int) marking the kind of contents of the channel queue, a queue of messages (of type QueueType( $\tau,\alpha$ )), and a queue of processes (of type QueueType(ProcType ( $\tau,\alpha$ ), $\alpha$ )). The flag can assume one of three different values: 0 indicates the channel queue is empty; 1 indicates at least one message enqueued; and 2 represents at least one enqueued process. The macros for manipulating channel queues are:

```

\begin{array}{c} \mathsf{ChannelQueueAlloc}(\tau,\alpha) \stackrel{\mathsf{def}}{=} \mathbf{malloc}[\mathsf{int}, \ \mathsf{QueueType}(\tau,\alpha), \\ \mathsf{QueueType}(\mathsf{ProcType}(\tau,\alpha), \ \alpha)] \\ \mathbf{guarded} \ \mathbf{by} \ \alpha \\ \\ \mathsf{ChannelQueueState}(r) \stackrel{\mathsf{def}}{=} r[0] \\ \mathsf{ChannelQueueMsgs}(r) \stackrel{\mathsf{def}}{=} r[1] \\ \mathsf{ChannelQueueProcs}(r) \stackrel{\mathsf{def}}{=} r[2] \\ \mathsf{CHANNEL\_QUEUE\_EMPTY} \stackrel{\mathsf{def}}{=} 0 \\ \mathsf{CHANNEL\_QUEUE\_WITH\_MSGS} \stackrel{\mathsf{def}}{=} 1 \\ \mathsf{CHANNEL\_QUEUE\_WITH\_PROCS} \stackrel{\mathsf{def}}{=} 2 \\ \end{array}

```

The creation of a channel queue, having register  $r_1$  type  $\mathsf{ProcType}(\mathsf{int}, \alpha)$  (as in the result of the previous example), is:

```

\begin{array}{lll} r_4 \coloneqq r_1 & -- \text{ we want to use } r_1 \text{ afterwards} \\ r_1 \coloneqq \text{ChannelQueueAlloc(int, } \alpha) & -- \text{ alloc the channel} \\ -- \text{ mark the channel as empty:} \\ \text{ChannelQueueState}(r_1) \coloneqq \text{CHANNEL\_QUEUE\_EMPTY} \\ \text{QueueCreateEmpty}(r_2, r_3, 0, \text{ int, } \alpha) & -- \text{ create an empty queue of integers} \\ \text{ChannelQueueMsgs}(r_1) \coloneqq r_2 & -- \text{ set the queue of messages as } r_2 \\ -- \text{ create an empty queue of processes; the sentinel is } r_4 \colon \\ \text{QueueCreateEmpty}(r_2, r_3, r_4, \text{ProcType(int,} \alpha), \alpha) \\ \text{ChannelQueueProcs}(r_1) \coloneqq r_2 & -- \text{ set the queue of processes as } r_2 \\ \end{array}

```

The last definition in this section, ChannelQueueCreate $(r, r_m, r_t, \tau, \alpha)$ , is the creation of a channel queue, where:

- r is the register that will refer the new empty channel of type Channel-QueueType $(\tau,\alpha)$ ;

- $r_q$  is the register that will hold the queue of processes of type Queue-Type(ProcType( $\tau,\alpha$ ), $\alpha$ );

- $r_e$  is the register that will point to the sentinel element of the queue of processes;

- v is a sentinel message of type  $\tau$ ;

- $\tau$  is the type of the transmitted messages;

- $\alpha$  is the lock protecting the channel.

```

\begin{array}{lll} {\sf ChannelQueueCreate}(r,r_q,r_e,v,\tau,\alpha) \stackrel{\sf def}{=} \\ r := {\sf ChannelQueueAlloc}(\tau,\alpha) & -- \ create \ the \ new \ channel \\ -- \ flag \ it \ as \ empty: \\ {\sf ChannelQueueState}(r) := {\sf CHANNEL\_QUEUE\_EMPTY} \\ -- \ create \ an \ empty \ queue \ of \ messages, \ where \ v \ is \ the \ sentinel : \\ {\sf QueueCreateEmpty}(r_q,r_e,v,\tau,\alpha) \\ {\sf ChannelQueueMsgs}(r) := r_q \qquad -- \ set \ the \ channel \ of \ messages \\ {\sf ProcCreateSentinel}(r_q,r_e,\tau,\alpha) \qquad -- \ create \ a \ dummy \ process \\ -- \ create \ a \ queue \ of \ processes, \ where \ the \ sentinel \ is \ in \ r_q: \\ {\sf QueueCreateEmpty}(r_q,r_e,r_q,{\sf ProcType}(\tau,\alpha),\alpha) \\ {\sf ChannelQueueProcs}(r) := r_q \qquad -- \ set \ the \ queue \ of \ processes \\ \end{array}

```

Notice that value v is unaltered in this macro. Furthermore, the value v may only be register  $r_q$ .

#### 4.2 Communication

In this section we list the two operations responsible for communications using channels: sendMessage and receiveMessage. The former sends a message through a channel. The latter expects a continuation, where the message will be received, and an environment (user data that is available in the continuation). In either case, when a thread jumps to any of these operations, it is not guaranteed that the processor will be yield, or continue executing. Both operations require exclusive access to the lock of the channel, since they alter its internal state, thus representing a point of contention (in regards to the protecting lock).

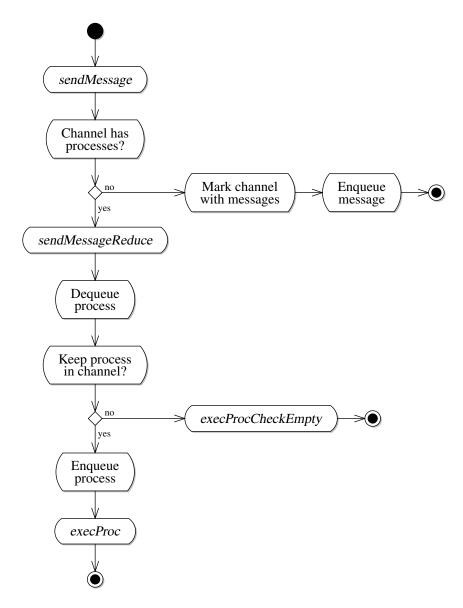

**Send message.** We define an operation to send a message through a channel queue (depicted in Figure 4.4):

```

sendMessage [\alpha, \tau] — the protecting lock and the message's type are abstracted

2

— the message being sent

3

r_2: ChannelQueueType(\tau,\alpha), — the target channel

r_3: \langle \mathsf{lock}(\alpha) \rangle^{\alpha})

-- the channel's lock

4

requires (\alpha;;) {

5

-- exclusive access to the

channel

6

r_4:= ChannelQueueState(r_2) -- get the state of the channel

7

-- verify if there are process waiting for a message

8

if r_4= CHANNEL_QUEUE_WITH_PROCS

9

—— when there are, deliver the message:

10

jump sendMessageReduce[\tau][\alpha]

11

-- else no processes in the channel, enqueue the message

12

13

—— flag the channel as containing messages:

14

ChannelQueueState(r_2) := CHANNEL\_QUEUE\_WITH\_MSGS

15

r_2:= ChannelQueueMsgs(r_2) -- get the queue of messages

16

QueueAdd(r_2,r_1,r_4,r_1,\tau,\alpha) — put the message (r_1) in the queue

17

-- unlock the channel's lock

unlockE r_3

yield

18

— release control of the processor

19 }

```

This operation either jumps to the code block sendMessageReduce, when there are processes waiting for a message to arrive, or yields the processor's control, after placing the message in the channel.

Figure 4.4: The activity diagram outlines the execution of sendMessage, where activities in italic represent code blocks (identified by their labels).

In the following, we list the code block sendMessageReduce. This code block assumes that there is at least one processes waiting for a message to arrive.

```

2

3

r_2: ChannelQueueType(\tau,\alpha), — the target channel

4

r_3: \langle \mathsf{lock}(\alpha) \rangle^{\alpha})

— the channel's lock

5

requires (\alpha;;)

-- exclusive access to \alpha

6

r_6:= ChannelQueueProcs(r_2) — moves the queue of processes to r_6

7

-- remove a process from the queue, and move it into r_4

8

--r_5 holds the number of processes in the queue:

9

QueueRemove(r_6, r_5, r_4)

10

-- check if the process is to be kept

r_7:= ProcKeep(r_4)

11

if r_7 = 0

12

—— do not keep it in channel, then deliver the message

13

jump execProcCheckEmpty[\tau][\alpha]

14

—— keep the process in the channel after delivery

15

-- move the message into r_7

r_7 := r_4

16

—— add process the back into the queue:

17

QueueAdd(r_6, r_7, r_8, r_4, ProcType(\tau, \alpha), \alpha)

18

-- deliver the message to the process (in r_4)

19

-- we are certain that the state of the channel is unaltered (with processes)

20

unlockE r_3

— no exclusive access needed

21

jump exec\mathsf{Proc}[\tau][\alpha]

— deliver the process

22 }

```

We begin by removing the process from the channel. After that, we verify if we need to put the process back in the channel, by verifying its keep in channel flag. We then jump to execProcCheckEmpty.

Next, is the code block execProcCheckEmpty:

8

execProcCheckEmpty  $[\alpha, \tau]$  — the protecting lock and the message's type are abstracted

```

-- the message being sent

2

r_2: ChannelQueueType(\tau,\alpha), — the target channel

3

4

r_3: \langle \mathsf{lock}(\alpha) \rangle^{\alpha},

— the channel's lock

r_4: ProcType(\tau, \alpha),

— the receiving process

5

6

r_5: int)

— the remaining processes

7

requires (\alpha;;) {

-- exclusive access to \alpha

```

```

9

—— verify if the channel became empty:

10

if r_5 = 0

11

—— the channel became empty, mark and then reduce:

12

jump execProcFirstEmpty[\tau][\alpha] -- mark it as empty and continue delivery

13

— no need to change the channel's state, continue with the reduction

14

15

-- we don't need access to the channel to deliver the message

16

unlockE r_3

17

jump execProc[\tau][\alpha]

18 }

```

The code block checks if the channel needs to be marked as empty, before delivering the message to the process (in code block code block execProc).

We depict code block execProcFirstEmpty:

```

1 execProcFirstEmpty [\alpha,\tau] — the protecting lock and the message's type are abstracted

```

```

2

(r_1: \tau,

— the message being sent

3

r_2: ChannelQueueType(\tau,\alpha), — the target channel

r_3: \langle \mathsf{lock}(\alpha) \rangle^{\alpha},

-- the channel's lock

4

r_4: ProcType(\tau,\alpha))

5

— the receiving process

requires (\alpha;;) {

-- exclusive access to the

6

channel

7

— mark the channel as empty:

ChannelQueueState(r_2) := CHANNEL_QUEUE_EMPTY

8

9

unlockE r_3 — we don't need access to the channel to deliver the message

10

jump execProc[\tau][\alpha]

```

where the state of the channel is marked as empty and then continues the delivery.

We present code block

11 }

```

execProc [\alpha, \tau] — the protecting lock and the message's type are abstracted

2

— the message being sent

(r_1: \tau,

3

r_2: ChannelQueueType(\tau,\alpha), — the target channel

4

r_3: \langle \mathsf{lock}(\alpha) \rangle^{\alpha},

-- the channel's lock

r_4: ProcType(\tau,\alpha)

5

— the receiving process

6

— spin lock to acquire the channel's lock:

7

r_5:= tslS r_3 -- we only need read access to the channel

8

if r_5 = 0

9

—— we have access, continue with the delivery:

```

```

\begin{array}{ll} 10 & \textbf{jump} \; \mathsf{execContinue}[\tau][\alpha] \\ 11 & -- \; \textit{try again:} \\ 12 & \textbf{jump} \; \mathsf{execProc}[\tau][\alpha] \\ 13 & \end{array} \}

```

The code block spins to get shared access to the channel's lock. Upon success it jumps to execContinue.

Following is a list of code block execContinue:

```

execContinue[\alpha,\tau] — the protecting lock and the message's type are abstracted

2

(r_1: \tau,

— the message being sent

3

r_2: ChannelQueueType(\tau,\alpha), — the target channel

4

r_3: \langle \mathsf{lock}(\alpha) \rangle^{\alpha},

-- the channel's lock

5

r_4: ProcType(\tau,\alpha))

— the receiving process

— shared access to the channel

6

requires (;\alpha;) {

7

r_4:= ProcClosure(r_4) — get the closure of the process

8

-- unpack it and get the type of the environment (\tau_e)

\tau_e, r_4:= unpack r_4

9

r_5 := r_3

-- move channel's lock into r_5

10

r_3:= ClosureLock(r_4) — get the packed lock of the environment

11

\beta, r_3:= unpack r_3

— unpack the lock of the environment

12

r_2:= ClosureEnv(r_4)

-- move the environment into r_2

13

r_4:= ClosureCont(r_4) — move the continuation into r_4

14

unlockS r_5

— we don't need more access to the channel's lock

15

—— try to get the lock of the environment, then continue delivery:

16

jump execProcGrabLock[\tau_e][\tau][eta]

17 }

```

The closure is unpacked, as well as the associated lock, and the lock of the channel released. After that, it jumps to execProcGrabLock, to get the lock of the environment.

We show the code block

1 execProcGrabLock  $[\alpha, \tau_m, \tau_e]$  — the protecting lock, the message's type, and the type of the environment are abstracted

```

2

— the message

(r_1: \tau_m,

3

r_2: \tau_e,

— the environment

—— the environment's lock

r_3: \langle \mathsf{lock}(\alpha) \rangle^{\alpha},

4

5

r_4: ContType(\tau_m, \tau_e)) { -- the continuation

6

—— spin lock to get the shared access:

r_5:= tslS r_3

8

if r_5 = 0

```

```

\begin{array}{lll} 10 & -- \ \textit{we have shared access, jump to continuation:} \\ 11 & \mathbf{jump} \ r_4[\alpha] \\ 12 & -- \ \textit{try again:} \\ 13 & \mathbf{jump} \ \mathrm{execProcGrabLock}[\tau_e][\tau_m][\alpha] \\ 14 & \end{array} \}

```

which is a spin lock (for a shared lock) that jumps to the continuation when it is successful.

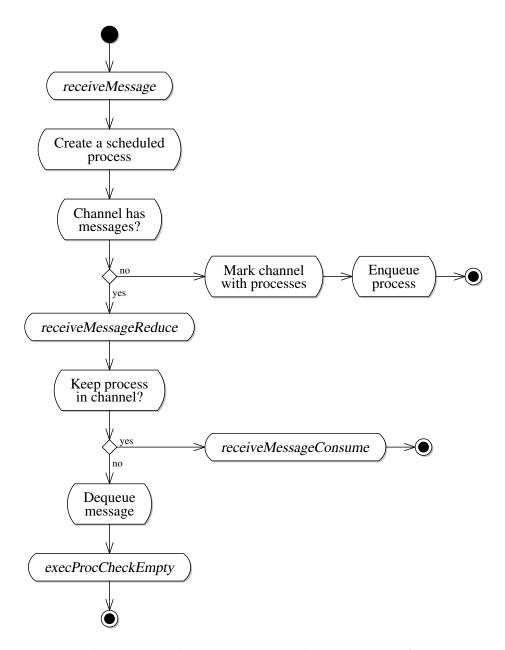

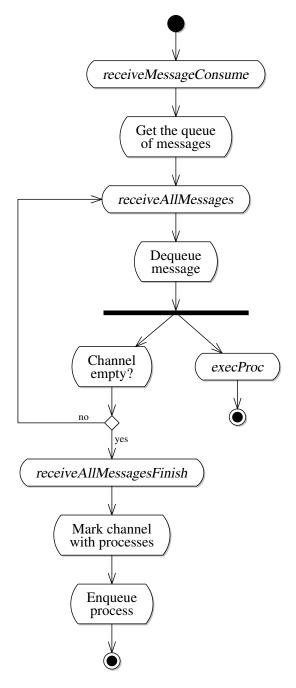

Receive a message. We describe receiveMessage, another core operation, where we schedule a process to receive a message. The outline of the algorithm, depicted by Figure 4.5, is to place the process in the buffer, if there are no messages to be delivered. Otherwise, we execute the process. When a process has the flag to keep in the channel queue set, all the messages in the channel queue are consumed by that process.

```

1

receiveMessage [\alpha, -- the lock of the channel,

2

\beta, — the lock of the environment,

3

au_m, -- the type of the message,

\tau_e] — and the type of the environment, are abstracted

4

5

(r_1: \mathsf{ContType}(\tau_m, \tau_e),

— the continuation

6

r_2: ChannelQueueType(\tau_m, \alpha), — the target channel

7

r_3: \langle \mathsf{lock}(\alpha) \rangle^{\alpha},

-- the channel's lock

8

-- the environment

r_4: \tau_e,

9

— the environment's lock:

10

r_5: \langle \mathsf{lock}(\beta) \rangle^{\beta},

11

—— the keep in channel flag:

12

r_6:int)

13

requires (\alpha;;) {

14

r_5:= packL \beta,r_5 as PLock() -- pack the environment's lock

15

r_7:= ClosureAlloc(\tau_m, \tau_e, \alpha) — alloc the closure

\mathsf{ClosureCont}(r_7) := r_1 -- \mathit{set the continuation}

16

17

ClosureEnv(r_7) := r_4 — set the environment

18

ClosureLock(r_7) := r_5 -- set the packed lock

19

r_7:= pack \tau_e, r_7 as ClosureType(\tau_m, \alpha) — abstract the environment of closure

r_4:= ProcAlloc(\tau_m, \alpha) — alloc a process

20

21

ProcClosure(r_4) := r_7 -- set the packed closure of the process

22

ProcKeep(r_4) := r_6 — set the keep on channel flag

23

-- test the state of the channel:

24

r_1:= ChannelQueueState(r_2)

```

Figure 4.5: The activity diagram outlines the execution of receiveMessage, where activities in italic represent code blocks (identified by their labels).

```

25

if r_1 = CHANNEL_QUEUE_WITH_MSGS

26

—— when there are messages, consume the message:

27

jump receiveMessageReduce[\tau_m][\alpha]

28

— otherwise enqueue the process

29

—— mark the channel with procs:

30

ChannelQueueState(r_2) := CHANNEL\_QUEUE\_WITH\_PROCS

31